基于AD6688+Arria10的5G JESD204B测试系统

本文将使用 ADI 最新的 AD6688 Development Kit 和 Intel 的 FPGA Arria10 gx Development Kit,搭建基于 lane rata 4.9512 G 的 JESD204B 测试环境。主要包括以下内容:

- 如何搭建基于ADI AD6688,Intel FPGA Arria10 的 JESD204B 测试环境与工程

- 基于测试环境,验证真实信号链路,进行接收数据的谱线分析

JESD204B 测试系统搭建

硬件平台

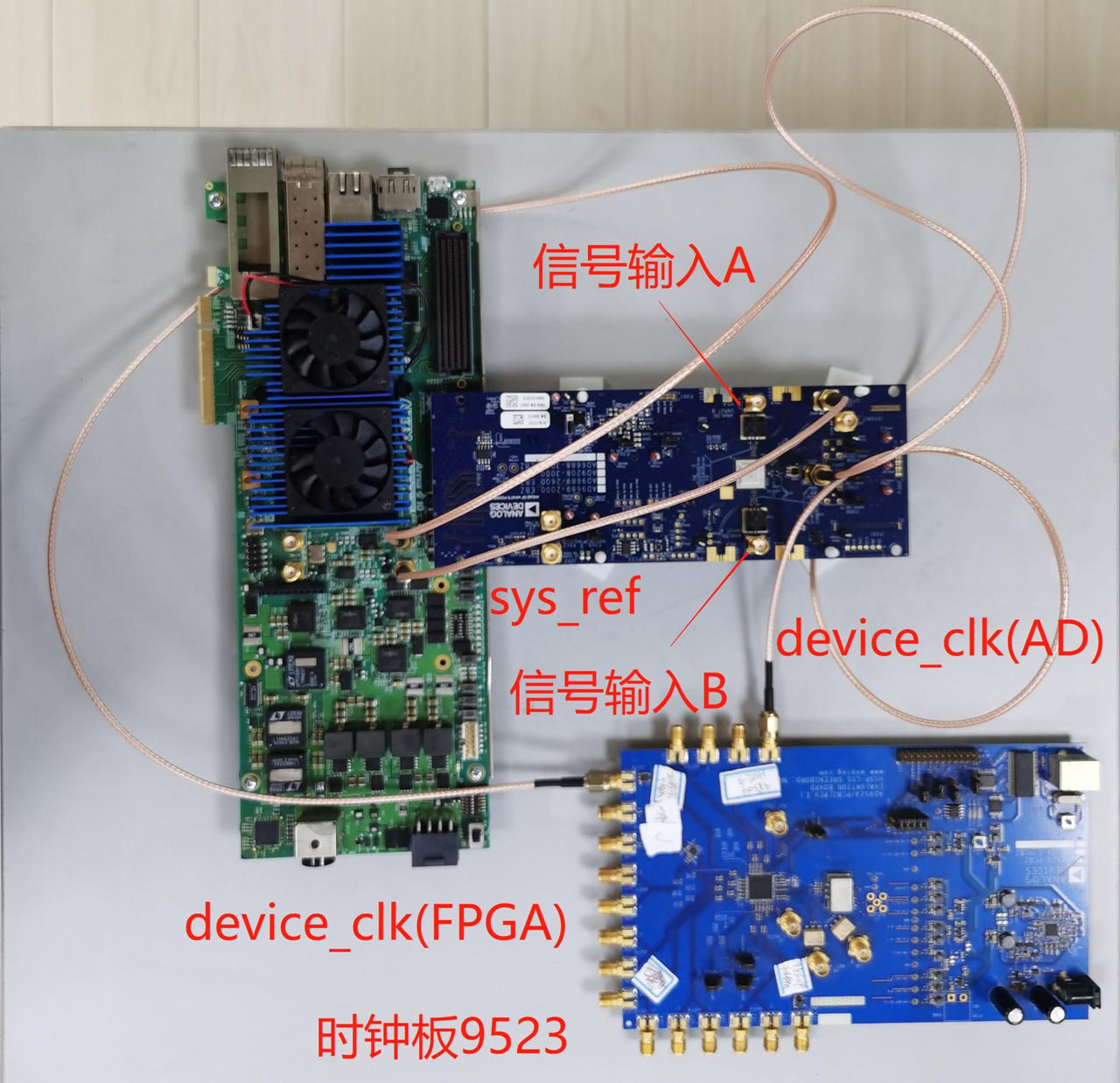

JESD204B 测试系统硬件说明,时钟体系和供电说明如下:

硬件说明

Arria10 FPGA Development Kit,AD6688 Development Kit,AD9523/PCBZ,若干同轴线缆。

时钟体系说明

AD9523/PCBZ:给系统提供同源时钟,其中给 AD 提供的 device clk: 983.04M,给 FPGA 提供的 device clk: 245.76M。

供电说明

AD6688 通过FMC接口与 FPGA 互联,供电通过 FPGA 提供,FPGA 单独供电。

JESD204B 测试系统搭建如下图(图1)所示:

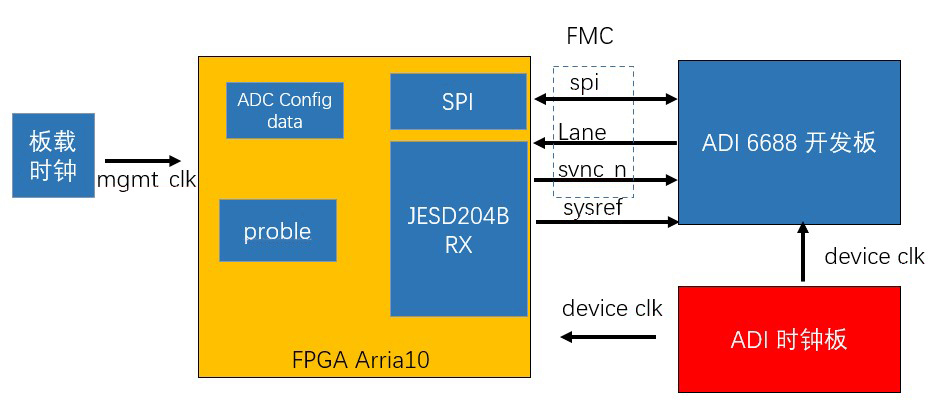

系统功能

JESD204B 测试系统包括了Proble模块、ADC Config data 模块、SPI 模块、JESD204B RX 以及 FMC 接口。

- Proble 模块:提供用户接口配置相关的寄存器值

- ADC Config data 模块:存储相关的ADC配置值, 切换SPI的用户配置模式与起电自动配置模式

- SPI 模块:SPI 功能模块,读写ADC 寄存器

- JESD204B RX:JESD204B 接收的最小功能单元

FMC 接口:主要包含SPI 相关信号线,204B数据信号线等

具体系统功能图如下所示:

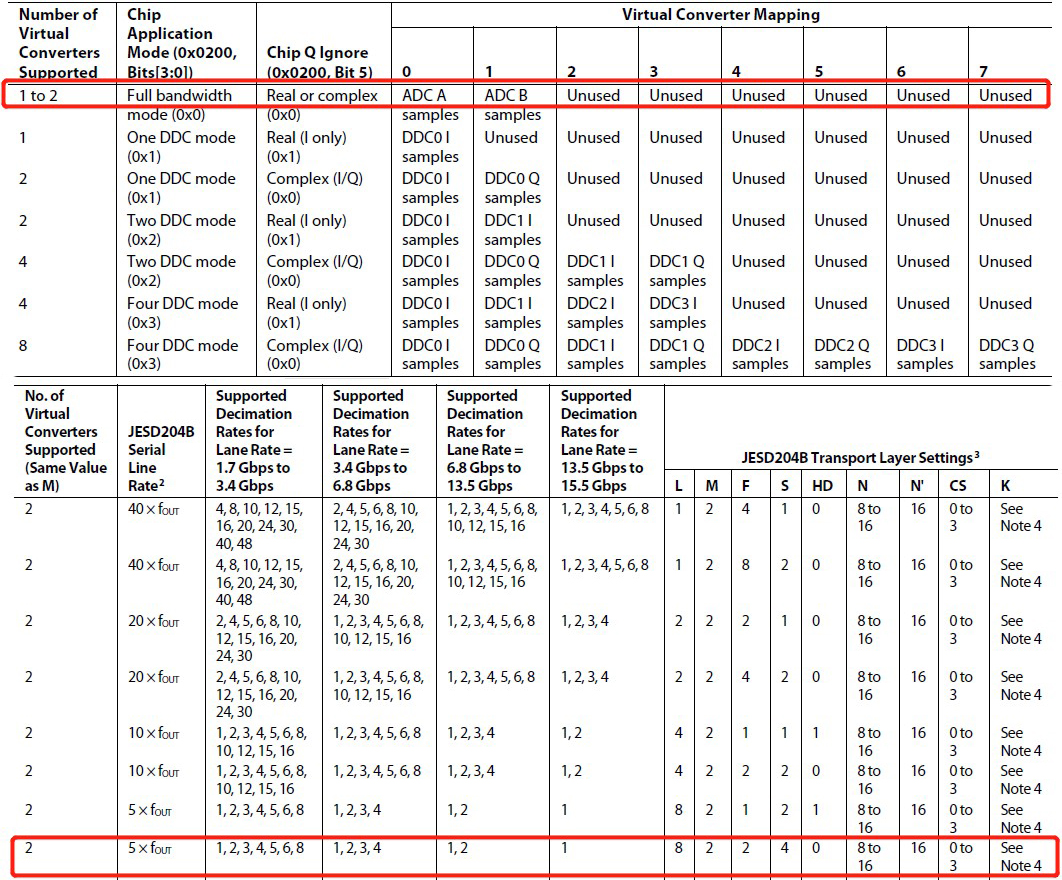

JESD204B 参数计算

ADI 选用模式,选用下图(图3)作为本次DEMO的链路参数:

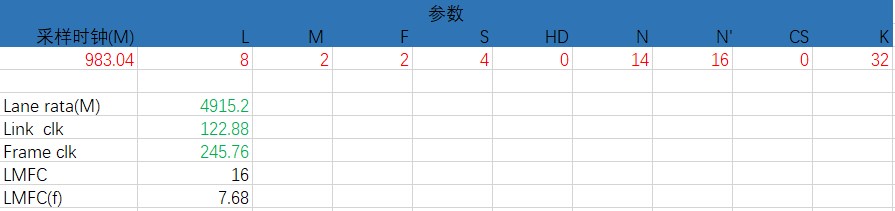

下图(图4)是 FPGA 链路的参数计算:

系统测试结果

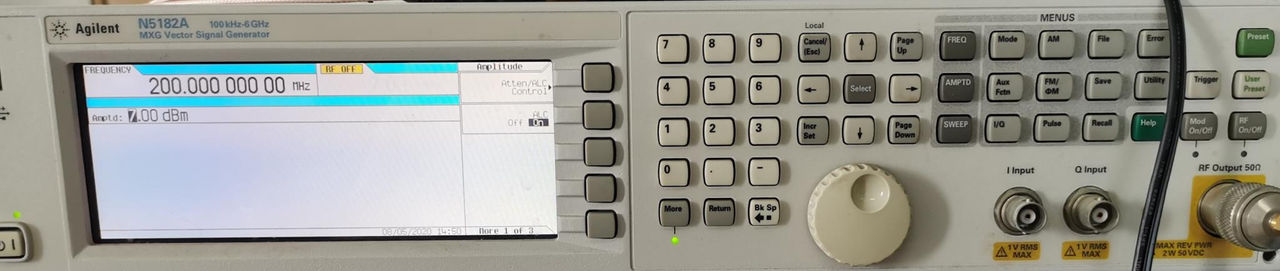

利用信号源输入200M 的单音信号给 AD6688,在 FPGA 侧收到相关的信号并使用 MATLAB 做频谱分析。

如下图(图5)所示:

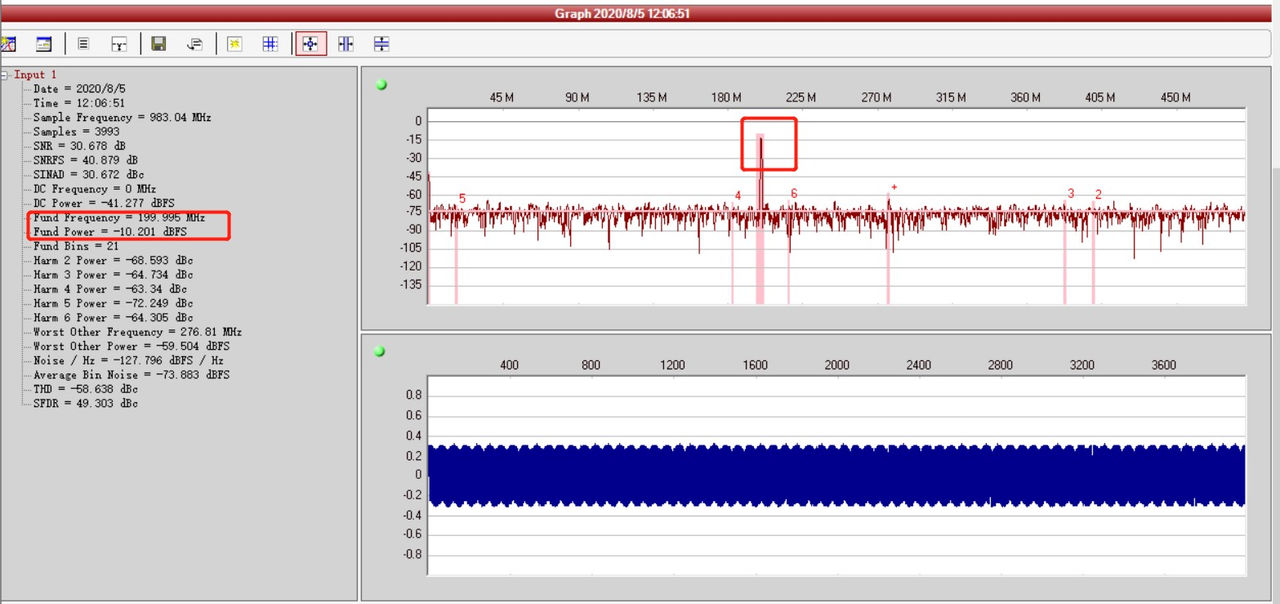

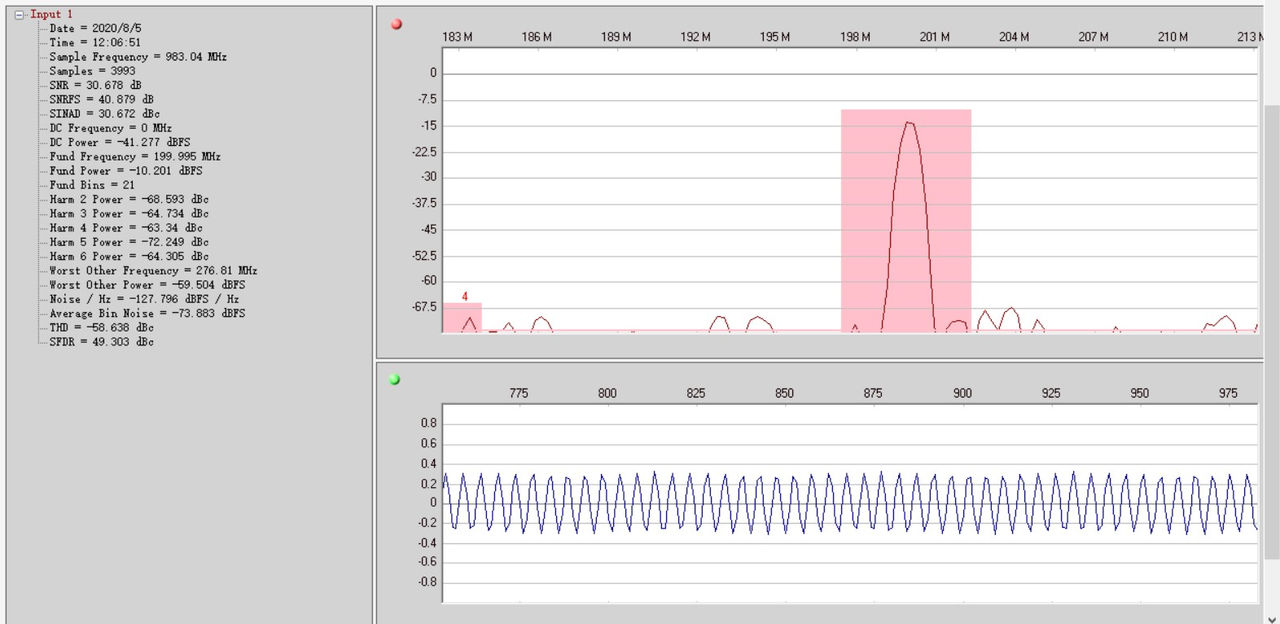

接收信号频域与时域信息

输入200M的单音信号给 AD6688 采样后,利用 JESD204B 传输给 FPGA,FPGA 将收到的数据,借助 ADI 的 VisualAnalog 软件做时序与频域分析。 如下图(图6、图7)所示:

系统测试说明

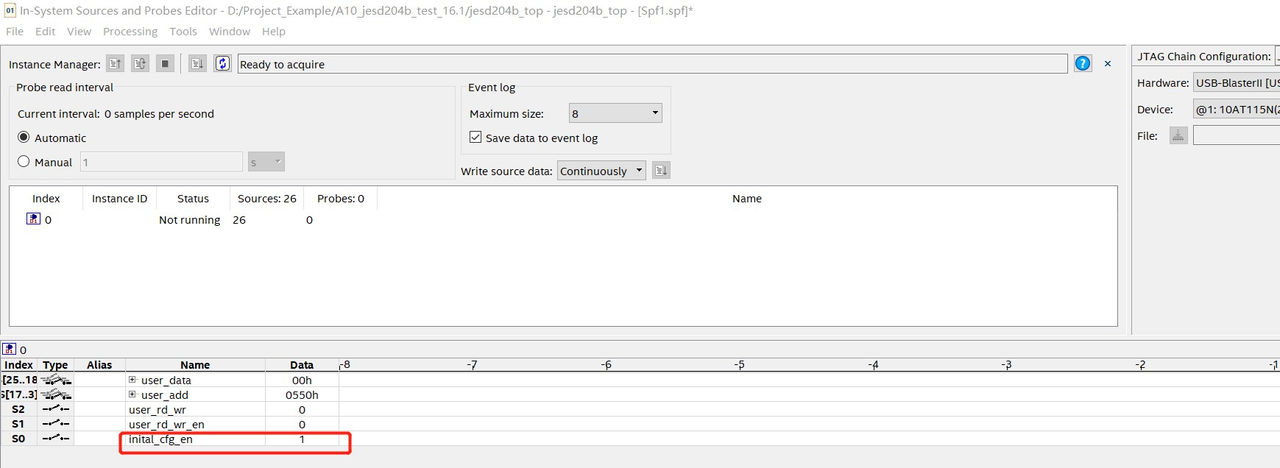

下载sof 文件后,使用Proble 功能给:inital_cfg_en 输入1,启动配置初始化(测试模式)。如下图(图8)所示:

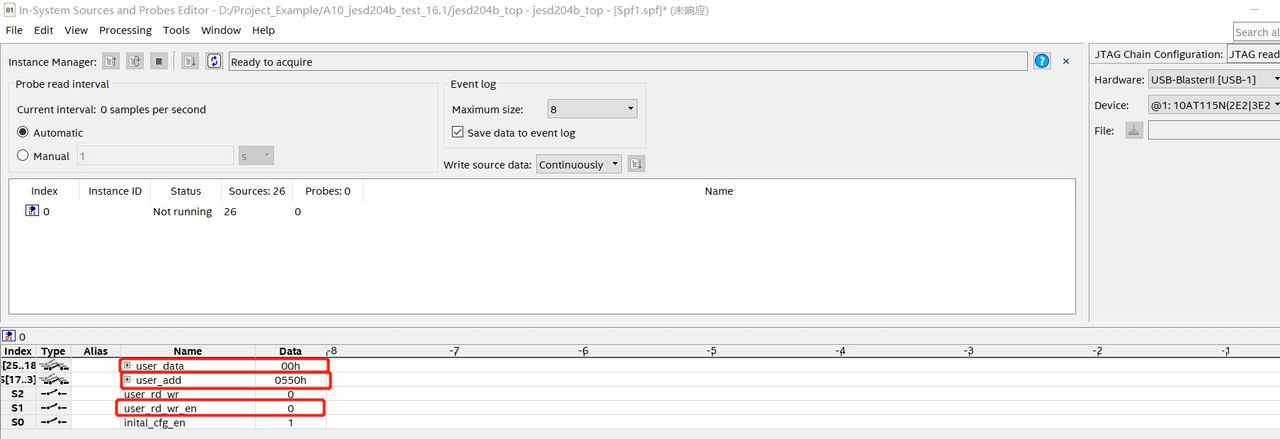

配置:user_data 为0x00, user_add 为0x0550, user_rd_wr_en 为0x1;切换为正常模式。如下图(图9)所示:

总结

本文主要阐述基于 Intel Arria10 FPGA 与 AD6688 如何进行测试环境的搭建,及器件性能指标的快速评估。上文提及的测试工程、AD的相关配置字、技术文档都可以分享给大家。欲了解相关DEMO板与测试工程、更多的技术细节及解决方案,您可以点击下方「联系我们」,提交您的需求,我们骏龙科技公司愿意为您提供更详细的技术解答。

相关阅读

更多信息:

微信平台

微信平台

FPGA 微信平台

FPGA 微信平台

領英 LinkedIn

領英 LinkedIn