解构Pipelined ADCs 架构与纠错原理

Pipelined ADC架构主导了现阶段采样率在5MSPS-10MSPS的主要应用。虽然flash架构的ADC主导了20世纪80年代和90年代的8位音频IC ADC市场,但是Pipelined架构在现代应用中已经很大程度上取代了flash ADC。在大于1GHz采样率的少量高功耗应用场合中flash仍然受到欢迎,但其分辨率只能达到6位或8位。

Pipelined ADC架构广泛应用于视频、图像处理、通信和工业领域。这种架构适合各种成本相对较低的集成电路工艺,如CMOS和Bi CMOS。目前的技术可以做到12bit~16bit 的分辨率,且采样率大于100MSPS。

Pipelined ADC基本结构

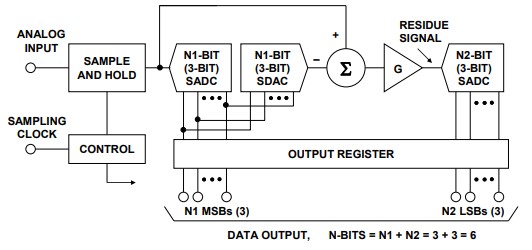

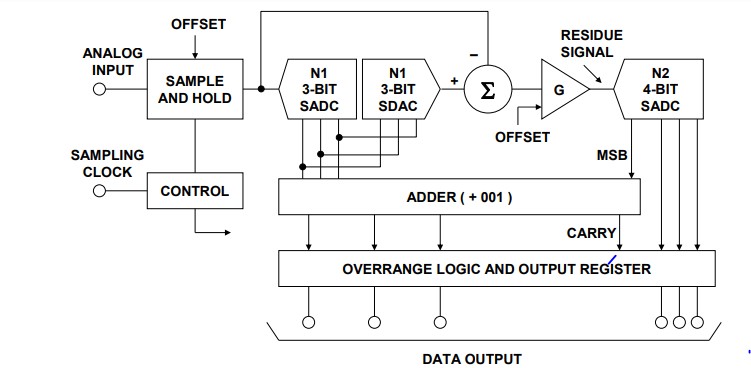

Pipelined ADC起源于20世纪50年代的排序结构ADC,第一次是被用来作为来减少flash ADC架构中的二极管数量和降低功耗的解决方案。如图1所示为一个6位两级排序结构的ADC基本架构。

输入采样保持(SHA)的输出由第一级3位子adc进行数字化(SADC)——flash转换器。然后将粗略的3位MSB使用3位sub-DAC (SDAC)转换回模拟信号。SDAC输出减去SHA输出,放大,并应用于第二阶段3位SADC。“剩余信号”是通过3位第二阶段SADC进行数字化,从而生成6位的三个LSB输出。这种类型的ADC通常被称为“子范围”,因为它的输入范围被细分为许多更小的范围(子范围),这些范围又被进一步细分。

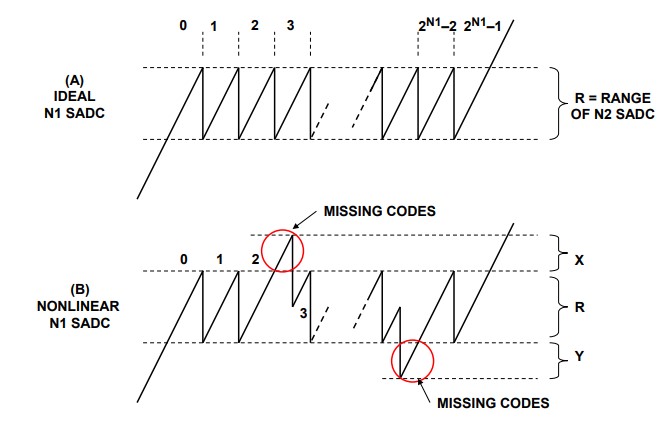

这个子范围ADC可以通过检查第二级ADC输入端的剩余波形来进行分析如图2所示。这个波形呈低频斜坡输入信号到整个ADC。为了不丢失代码,剩余波形必须准确地填充第二阶段ADC的输入范围,如图2a所示。这意味着N1的SADC和N1的SDAC都必须比N1 + N2位准确。在这个例子中,N1 = 3, N2 = 3, N1 + N2 = 6。这个体系结构,如图2b所示,是有用的分辨率高达8位(N1 = N2 = 4),但维护优于8位这两个阶段(特别是温度变化过大的阶段)之间的协调是很困难的。如图2B所示,当残差波形失效时,会导致代码缺失在N2 SDAC,“R”,并且属于“X”或“Y”区域。该问题是由一个N1 SADC或级间增益和/或偏移不匹配引起的。

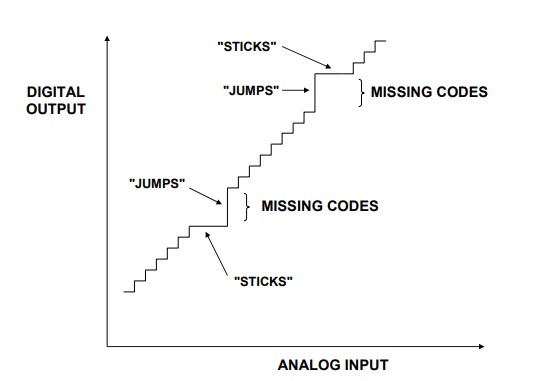

当级间对齐不正确时,缺失的代码将出现在整个ADC中传递函数如图3所示。如果剩余信号进入正超量程("X"区域),输出首先“粘住”一个代码,然后“跳过”一个区域,留下缺失的代码。如果剩余信号为负超量程,则发生反向。

在这一点上值得注意的是,没有特别的原因,除非某些设计问题在这个讨论的范围之外,子界架构中每个阶段的比特数必须相等。此外,还可以有两个以上的阶段。无论如何,图1中所示的体系结构被限制为大约8位的分辨率,除非有某种形式增加了纠错的功能。

带数字纠错的分段ADC

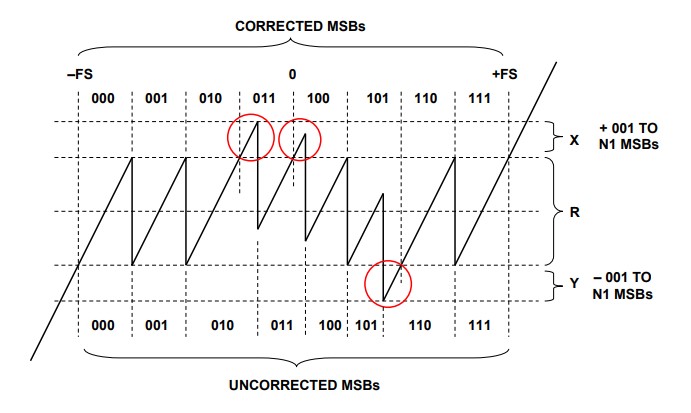

为了可靠地利用子排序方法实现高于8位的分辨率,该技术一般称为数字校正子测距、数字纠错、利用重叠位、冗余位等。这种方法早在由T.C.Verster于1964年出版的A Method to Increase the Accuracy of Fast Serial-Parallel Analog-to-Digital Converters就有提及,并迅速被广泛传播和应用。如图4所示的剩余波形说明了基本概念。

剩余波形显示为N1 = 3位的特定情况。在一个标准的子排序中ADC的残余波形必须完全填充N2 SADC的输入范围,必须保持在指定的区域R内,缺失的代码问题通过添加额外的量化来解决电平在正超量程区域X和负超量程区域y。在基本的N2 FLASH SADC中,电平需要额外的比较器。该方案的工作原理如下。一旦残留物进入X区域,N2 SADC应返回全零并开始计算。此外,代码001必须添加到N1 SADC的输出中,以使msb读取了正确的代码。图的下方标示了未校正的MSB区域波形和位于波形的上部校正后的MSB区域。类似的,当剩余波形进入负超量程区域y时,就会发生Y区域的第一个量化级应该生成全1码这种情况,而其他的超量程比较器应使计数减少。在“Y”区域,代码001必须为从MSB中减去正确的MSB代码。理解这一点很重要为了使这种校正方法正常工作,N1 SDAC必须等于ADC的总分辨率。N1型SDAC的非线性或增益误差会影响振幅的垂直“跳”部分的残留波形,因此在输出端可以产生缺失的代码。

现代数字校正子范围adc通常通过对N2 SADC使用一个具有更高分辨率的内部ADC获得额外的量化级,。例如,如果在N2 SADC中添加额外的1位,其范围将增加一倍,然后剩余波形就可以超出N1 SADC的1 / 2 LSB范围。如果增加两个额外的位N2,就可以使剩余波形超出N1 SADC参考的1½lbs范围。。残余波形是使用Horna的技术,这样只需要一个简单的加法器来执行校正逻辑。这一切是如何运作的细节并不是显而易见,最好通过一个6bit的实际例子来解释。ADC具有一个3位MSB SADC和一个4位LSB SADC,提供一位错误纠正。示例ADC的框图如图5所示。

信号经过输入采样保持后,由3位SADC进行数字化,由3位SDAC重构,减去持有的模拟信号,然后放大和适用于第二个4位SADC。选择放大器G的增益,使得剩余波形占4位SADC的输入范围的½。6位输出数据的3个lsb字直接从第二个SADC到输出寄存器。4位SADC的MSB控制加法器是否将001添加到3个msb中。加法器的进位输出与一些简单的超量程逻辑结合使用,以防止输出位返回数据在输入信号超出ADC的正范围时变成全零状态。

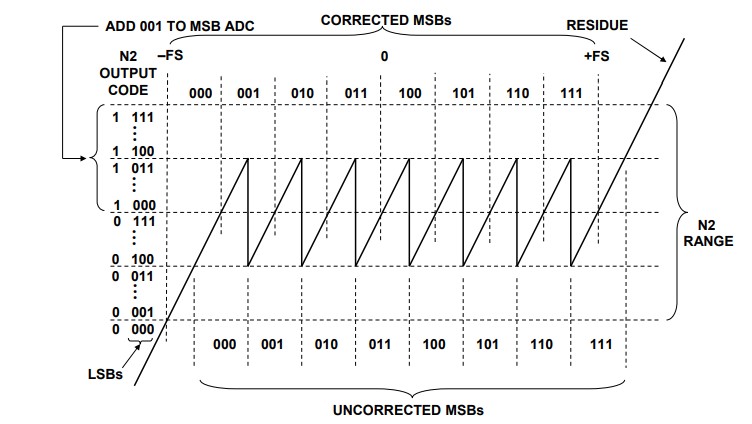

现在将对满量程斜坡输入的剩余波形进行更详细的检查来解释修正逻辑是如何工作的。图6显示了假设完美的理想剩余波形在第一个ADC的线性和两个阶段之间的完美对齐。注意残余波形恰好占到N2 SADC范围的½。SADC N2 的4位数字输出的在图的左侧显示。由SADC 的3位定义的未校正区域显示在图的底部。3位定义的区域修正后的N1显示在图的顶部。

从左到右跟随剩余波形,输入首先进入整个ADC范围在-FS, N2 SADC从0000开始计数,当N2 SADC达到1000后将 001添加到N1 SADC输出中,导致其从000更改为001。随着残留波形持续增加,N2 SADC持续计数直至达到代码1100,此时N1 SADC切换到下一级,SDAC切换和使剩余波形跳到0100输出码。加法器现在已禁用。因为N2 SADC的MSB为零,所以N1 SADC的输出仍为001。然后波形继续通过剩余的每个区域,直到到达+FS。

这个方法有一些值得提及的聪明特性。首先,整体传递函数为偏移1/ 2 LSB指的是MSB的SADC(这是1/16 FS指的是整个ADC 模拟输入)。这很容易通过向输入的采样保持中注入偏移量来纠正。众所周知,内部N1 SADC和SDAC发生切换点是最有可能产生额外的噪声,并且在整体上最有可能产生微分非线性ADC传递函数。以1/16 FS抵消它们,确保低电平信号(小于±1/16 FS)接近零伏特模拟输入。在临界开关点给出低噪音和优良的DNL,在通信应用是很有必要的。最后,由于理想的残差信号集中在N2 SADC的范围内,额外的N2 SADC提供的范围允许在N1 SADC转换中有±1/16 FS误差的同时保持没有丢失的代码。

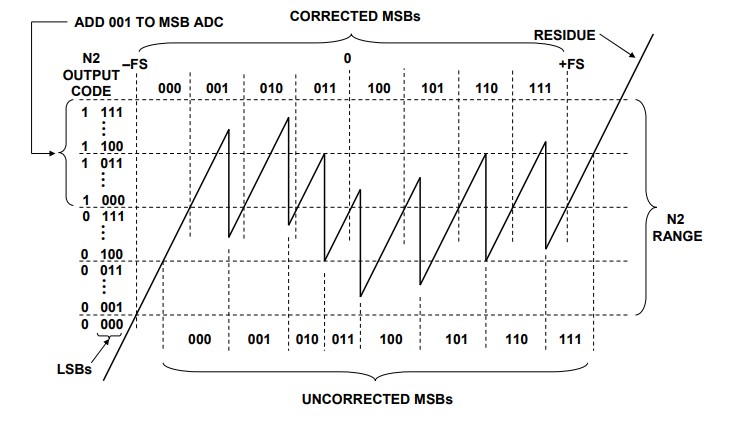

图7显示了在N1 SADC中存在错误的残余信号。注意,如果残余信号保持在N2 SADC信号的范围内,则对整体ADC线性度没有影响。只要满足此条件,所述的误差校正方法即可进行校正以下错误:采样保持下垂错误、采样保持稳定时间错误、N1 SADC增益误差,N1 SADC偏移误差,N1 SDAC偏移误差,N1 SADC线性误差,剩余放大器偏置误差。尽管它有能力纠正所有这些错误,但此方法不能校正与N1相关的增益和线性误差残差放大器的增益误差。这些参数中的误差必须保持1个LSB。从另一个角度来看,要认识到振幅的垂直“跳变”的残余跃迁与N1 SADC和SDAC变化水平相对应的波形必须保持在±½范围内。LSB引用N2 SADC输入以进行校正,以防止代码丢失。

图5所示的经过错误纠正的子范围ADC没有“流水线”延迟。当输入SHA保持第一阶段SADC作出决策,其产出由第一阶段SDAC进行重构,SDAC输出减去SHA输出,由SADC第二阶段放大数字化。数字数据经过错误校正逻辑和输出寄存器后,转换器就准备好接受另一个采样时钟输入。

总结

在高采样率的地方,流水线式的ADC架构几乎占主导地位。在采样率为2-5MSPS的区域使用SAR体系结构和流水线架构均可以,但具体使用哪个架构更合适需要根据实际应用来决定。

从8位到16位的分辨率在各种包和配置(信号,二元组、三元组、四边形等)。FINE-LINE CMOS工艺是目前最流行的工艺。而BiCMOS更多应用在需要获得最终的动态的性能的场合。

对于给定的采样率和分辨率,流水线式adc通常用它们来区分动态性能。例如,AD9244 14位,65 MSPS ADC被优化处理输入信号从直流到奈奎斯特(fs/2),功耗仅为550毫瓦。如果信号在更高的奈奎斯特区域,AD9445 14位,125 MSPS ADC则更合适,其功耗高达2.6W.

为特定的应用选择合适的流水线ADC不仅需要了解系统需求,还要了解体系结构的工作方式以及其它可能的权衡。简单地将ADC视为一个“黑盒子”通常会导致错误的选择。

参考文献

- A 12-bit 50MSPS Two-Stage A/D Converter——Roy Gosser and Frank Murden

- High Speed Analog-to-Digital Converter——J. L. Fraschilla, R. D. Caveney, and R. M. Harrison

- A 150Mbps A/D and D/A Conversion System——O. A. Horna

- High-Performance Parallel-Serial Analog to Digital Converter with Error Correction——G. G. Gorbatenko

- A Method to Increase the Accuracy of Fast Serial-Parallel Analog-to-Digital Converters——T. C. Verster

更多信息:

微信平台

微信平台

FPGA 微信平台

FPGA 微信平台

領英 LinkedIn

領英 LinkedIn